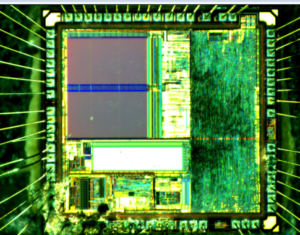

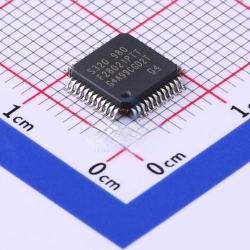

TMS320F28021 DSP Microprocessor Flash Memory Unlocking starts from disable the fuse bit of TMS320F28021 using dsp controller cracking technique, and then readout embedded firmware from MCU tms320f28021;

The C28x™ DSP generation is the newest member of the TMS320C2000™ DSP platform. The C28x is a very efficient C/C++ engine, enabling users to develop not only their system control software in a high-level language, but also enables math algorithms to be developed using C/C++.

The C28x is as efficient in DSP math tasks as it is in system control tasks that typically are handled by microcontroller devices. This efficiency removes the need for a second processor in many systems for the sake of dsp microcontroller tms320f28016 firmware extraction. The 32 x 32-bit MAC capabilities of the C28x and its 64-bit processing capabilities, enable the C28x to efficiently handle higher numerical resolution problems that would otherwise demand a more expensive floating-point processor solution.

Add to this the fast interrupt response with automatic context save of critical registers, resulting in a device that is capable of servicing many asynchronous events with minimal latency which can be used for reading microprocessor tms320f28015 flash binary.

The C28x has an 8-level-deep protected pipeline with pipelined memory accesses. This pipelining enables the C28x to execute at high speeds without resorting to expensive high-speed memories. Special branch-look-ahead hardware minimizes the latency for conditional discontinuities. Special store conditional operations further improve performance.