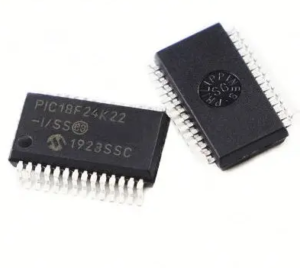

Replicating Encrypted MCU PIC18F24K22 Locked Flash Program from cracked microcontroller pic18f24k22 memory and copy it to new MCU pic18f24k22 for functionality recovery.

The OSCCON, OSCCON2 and OSCTUNE registers (Register 2-1 to Register 2-3) control several aspects of the device clock’s operation, both in full-power operation and in power-managed modes to readout pic18f45k20 microcontroller flash memory.

- Main System Clock Selection (SCS)

- Primary Oscillator Circuit Shutdown (PRISD)

- Secondary Oscillator Enable (SOSCGO)

- Primary Clock Frequency 4x multiplier (PLLEN)

- Internal Frequency selection bits (IRCF, INTSRC)

- Clock Status bits (OSTS, HFIOFS, MFIOFS, LFIOFS. SOSCRUN, PLLRDY)

Power management selection (IDLEN)

The System Clock Select bits, SCS<1:0>, select the main clock source. The available clock sources are

- Primary clock defined by the FOSC<3:0> bits of CONFIG1H. The primary clock can be the primary oscillator, an external clock, or the internal oscillator block.

- Secondary clock (secondary oscillator)

Internal oscillator block (HFINTOSC, MFINTOSC and LFINTOSC).

The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared to select the primary clock on all forms of Reset.