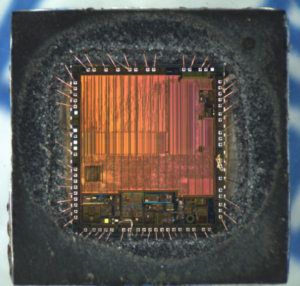

Renesas Microprocessor R5F21226DFP Flash Content Reading starts from cracking renesas R5F211A2SP microcontroller flash memory security fuse bit, and then dump renesas r5f212a7sdfa protected mcu program out from its flash memory;

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve ‘0’ bits and a Stop bit to extract secured renesas microcontroller r5f212a7sd code. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data.

Note that the value of data written to TXREG will be ignored and all ‘0’s will be transmitted. The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence by reading out renesas microprocessor r5f212aasd binary file. The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmis- sion. See Figure 16-9 for the timing of the Break character sequence.

8 bits × 1 (with 8-bit prescaler)

Timer mode (period timer), pulse output mode (output level inverted every period), event counter mode, pulse width measurement mode, pulse period measurement mode.

8 bits × 1 (with 8-bit prescaler)

Timer mode (period timer), programmable waveform generation mode (PWM output), programmable one-shot generation mode, programmable wait one- shot generation mode