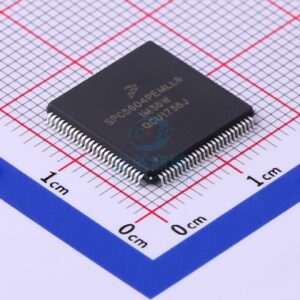

Freescale MCU SPC5601DF1MLL4 Flash Code Extraction needs to disable the protection over microprocessor SPC5601DF1MLL4 and then readout on chip flash content, the whole process will needs to crack tamper resistance system of processor SPC5601DF1MLL4;

Single issue, 32-bit CPU core complex (e200z0h)

Compliant with the Power Architecture® embedded category

Includes an instruction set enhancement allowing variable length encoding (VLE) for code size footprint reduction. With the optional encoding of mixed 16-bit and 32-bit instructions, it is possible to achieve significant code size footprint reduction.

Up to 256 KB on-chip Code Flash supported with Flash controller and ECC

64 KB on-chip Data Flash with ECC

Up to 16 KB on-chip SRAM with ECC

Interrupt controller (INTC) with multiple interrupt vectors, including 20 external interrupt sources and 18 external interrupt/wakeup sources by extract ic chip code

Frequency modulated phase-locked loop (FMPLL)

Crossbar switch architecture for concurrent access to peripherals, Flash, or SRAM from multiple bus masters;

Boot assist module (BAM) supports internal Flash programming via a serial link (CAN or SCI)

Timer supports input/output channels providing a range of 16-bit input capture, output compare, and pulse width modulation functions (eMIOS-lite)

Up to 33 channel 12-bit analog-to-digital converter (ADC)

2 serial peripheral interface (DSPI) modules

3 serial communication interface (LINFlex) modules

LINFlex 1 and 2: Master capable

LINFlex 0: Master capable and slave capable; connected to eDMA

1 enhanced full CAN (FlexCAN) module with configurable buffers