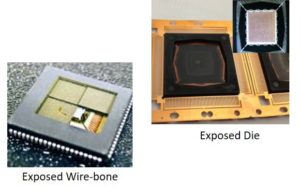

Protected Microprocessor dsPIC30F6012A Embedded Heximal Reading

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit to facilitate the process of Read Out Secured Heximal

This mode would typically be used in RS-485 systems which is a critical part for the process of Read Out Software of MCU Processor dsPIC30F5015.

This document contains device specific information for the PIC16F91X. Additional information may be found in the “PICmicro® Mid-Range MCU Family Reference Manual” (DS33023), downloaded from the Microchip web site.

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured

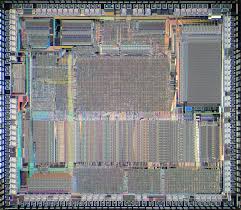

We can Reading Locked PIC16F916 Flash, please view the PIC16F916 features for your reference: In Slave mode, the data is transmitted and received as the external clock pulses

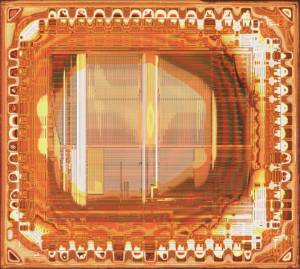

We can read out Program from MCU dsPIC30F3013, please view the MCU dsPIC30F3013 features for your reference: If a transmit was in progress when the bus collision

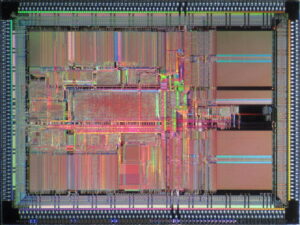

We can Read Out Microcontroller PIC16F690 Program, please view the Microcontroller PIC16F690 features for your reference: The SSP consists of a transmit/receive shift register (SSPSR) and a