Read Protected TMS320LF2403AP MCU Flash Memory is a process to restore dsp microprocessor tms320lf2403ap memory program, and clone heximal data to new microcontroller dsp tms320lf2403ap flash memory;

An emulator trap. This interrupt can be generated with either an INTR instruction or a TRAP instruction.

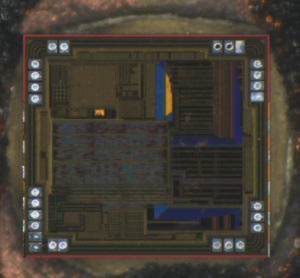

The reset operation ensures an orderly startup sequence for the device. There are two possible causes of a reset, as shown in below Figure.

![]()

The two possible reset signals are generated as follows:

Watchdog timer reset. A watchdog-timer-generated reset occurs if the watchdog timer overflows or an improper value is written to either the watchdog key register or the watchdog control register. (Note that when the device is powered on, the watchdog timer is automatically active.) The watchdog timer reset is reflected on the external RS pin

Reset pin To generate an external reset pulse on the RS pin, a low-level pulse duration of at least one CPUCLK cycle is necessary to ensure that the device recognizes the reset signal when unlocking secured dsp mcu tms320lf2406ap flash memory.

Once watchdog reset is activated, the external RS pin is driven (active) low for a minimum of eight CPUCLK cycles. This allows the TMS320x24x device to reset external system components.

The occurrence of a reset condition causes the TMS320x24x to terminate program execution and affects various registers and status bits to readout tms320f28015 microprocessor binary file. During a reset, RAM contents remain unchanged, and all control bits that are affected by a reset are initialized to their reset state.