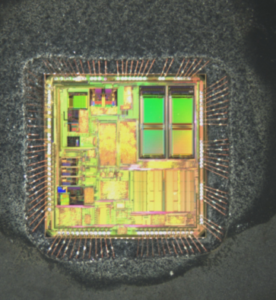

Secured Microcontroller TMS320LF2407AP Heximal Code Extraction will reset the fuse bit of locked MCU TMS320LF2407AP flash memory by decryption, and then duplicate embedded firmware program to new microprocessor tms320lf2407ap;

Hardware-generated interrupts are requested by external pins or by on-chip There are two types:

− External interrupts are generated by one of four external pins corresponding to the interrupts XINT1, XINT2, PDPINT, and NMI. The first three can be masked both by dedicated enable bits and by the CPU’s interrupt mask register (IMR), which can mask each maskable interrupt line at the DSP core when cracking protected dsp microcontroller tms320lf2401ap.

NMI, which is not maskable, takes priority over peripheral interrupts and software-generated interrupts. It can be locked out only by an already executing NMI or a reset.

− Peripheral interrupts are initiated internally by these on-chip peripheral modules: the event manager, SPI, SCI, WD, CAN, and ADC. They can be masked both by enable bits for each event in each peripheral and by the CPU’s IMR, which can mask each maskable interrupt line at the DSP core.

Software-generated interrupts for the F243/F241 devices include:

− The INTR instruction. This instruction allows initialization of any F243/F241 interrupt with software. Its operand indicates the interrupt vector location to which the CPU branches. This instruction globally disables maskable interrupts (sets the INTM bit to 1).

− The NMI instruction. This instruction forces a branch to interrupt vector location 24h, the same location used for the nonmaskable hardware interrupt NMI when unlock protected dsp tms320lf2402ap microcontroller. NMI can be initiated by driving the NMI pin low or by executing an NMI instruction. This instruction globally disables maskable interrupts.