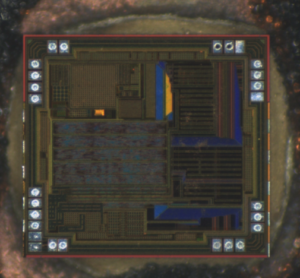

DSP Microprocessor TMS320F243FN Flash Program Extraction needs to attack security system of microcpu tms320f243fn and dsp controller tms320f243fn can be copied to new microcontroller;

External input / output space wait state. ISWS determines that between 0 to 7 wait states are applied to all reads and writes to off-chip I / O space. The memory cycle can be further extended by using the READY signal. The READY signal does not override the wait states generated by ISWS. These bits are set to 1 (active) by reset (RS).

Bus visibility modes. Bits 10 and 9 allow selection of various bus visibility modes while running from internal program and/or data memory. These modes provide a method of tracing internal bus activity in the process of dsp controller tms320f241pga code extraction. These bits are set to 11b by reset (RS), causing internal program address and program data to be output on the external address and data pins.

The F243 has a total of 32 general-purpose, bidirectional, digital I/O (GPIO) pins that function as follows: six pins are dedicated I/O pins (see Table 7) and 26 pins are shared between primary functions and I/O. The F241 has 26 I/O pins; all are shared with other functions.

The digital I/O ports module provides a flexible method for controlling both dedicated I/O and shared pin functions. All I/O and shared pin functions are controlled using eight 16-bit registers. These registers are divided into two types:

- Output Control Registers — used to control the multiplexer selection that chooses between the primary function of a pin or the general-purpose I/O function and flash program duplication from tms320f241fga microcontroller.

Data and Control Registers — used to control the data and data direction of bidirectional I/O pins.