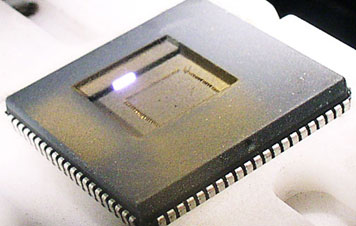

Altera CPLD IC EPM7128ELC84-10 Eeprom Content Restoration will start from attack CPLD EPM7128ELC84 security fuse bit, and then restore embedded jed firmware from eeprom of cpld epm7128elc84 chipset;

High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX® architecture 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 which has provide convenience for Attack PLD EPM7128ELC84-10 Binary.

Joint Test Action Group (JTAG) interface available in MAX 7000S devices – ISP circuitry compatible with IEEE Std. 1532

Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

Built-in JTAG boundary-scan test (BST) circuitry in MAX 7000S devices with 128 or more macrocells by decapsulate cpld chip epm7064aetc100 silicon package;

Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2) 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect).

Software design support and automatic place-and-route provided by Altera’s development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest for unlocking cpld chip epm7064stc44 memory.

Programming support

– Altera’s Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

– The BitBlasterTM serial download cable, ByteBlasterMVTM parallel port download cable, and MasterBlasterTM serial/universal serial bus (USB) download cable program MAX 7000S devices