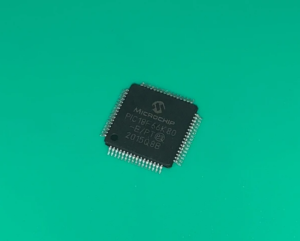

Decode Secured Microchip MCU PIC18F66K80 Memory Program means the protection over microcontroller pic18f66k80 will be unlocked in order to restore the embedded firmware from pic18f66k80 flash memory:

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for an EC or HS mode. If not, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

When PRI_IDLE mode is selected, the designated pri- mary oscillator continues to run without interruption in order to faciliate the process of microprocessor pic18f2553 heximal decoding. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC_RUN and SEC_I- DLE), the SOSC oscillator is operating and providing the device clock. The SOSC oscillator may also run in all power-managed modes if required to clock SOSC. In RC_RUN and RC_IDLE modes, the internal oscillator provides the device clock source.

The 31 kHz LF-INTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 28.2 “Watchdog Timer (WDT)” through Section 28.5 “Fail-Safe Clock Monitor” for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).