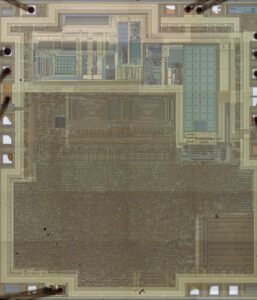

Copy Microchip Processor PIC18F14K50 Memory Heximal starts from crack mcu pic18f14k50 tamper resistance system, break off pic18f14k50’s fuse bit to download the firmware from flash memory;

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

In all Idle modes, a clock is provided to the peripherals. That clock could be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See Section 19.0 “Power-Man- aged Modes” for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

When MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller:

- from Sleep, in slave mode

- from Idle, in slave or master mode

If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

In SPI master mode, when the Sleep mode is selected, all module clocks are halted and the transmis- sion/reception will remain in that state until the devices wakes to copy mcu pic18f2620 binary file. After the device returns to RUN mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.