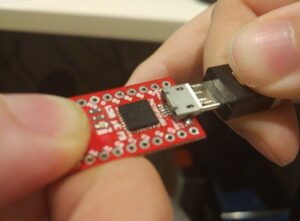

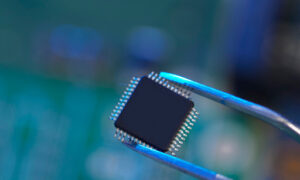

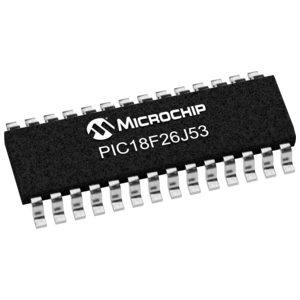

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep when Read MCU ATTINY88 Heximal. Once the word is received, the RSR register will transfer the data to the RCREG register by Read PIC18F26J53 Microcontroller Flash Program.

If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction of Break IC Software. If the GIE bit is also set, the program will branch to the interrupt vector.

Set the SYNC and SPEN bits and clear the CSRC bit.

Clear the ANSEL bit for both the CK and DT pins (if applicable).

If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register from Read IC ATTINY48A Heximal.

If 9-bit reception is desired, set the RX9 bit.

Set the CREN bit to enable reception.

The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

Retrieve the 8 Least Significant bits from the receive FIFO by reading the RCREG register through Read Chip ATMEGA128A Eeprom.

If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the neces- sary signals to run the Transmit or Receive Shift registers during Sleep after Read Microcontroller ATMEGA16PA Heximal. Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.