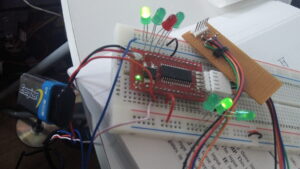

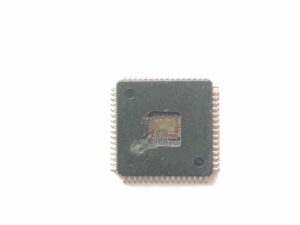

Copy Microchip PIC18F26J11 Memory Firmware from its flash program memory and eeprom data memory, the fuse bit of microcomputer microchip pic18f26j11 will be deciphered, the embedded source code will be duplicated from microchip mcu pic18f26j11;

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line when Copy Microchip PIC18F26J11 Memory Firmware. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation.

Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle for the purpose of Copy IC SN8P2606 Binary. Only as many clock cycles should be received as there are data bits.

If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared by MCU Recovering.

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO after Copy Microcontroller ATMEGA1281 Program. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten.

The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition when Copy Microchip PIC18F26J11 Memory Firmware.

If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register when Copy MCU SN8P2608 Heximal or by clearing the SPEN bit which resets the EUSART.