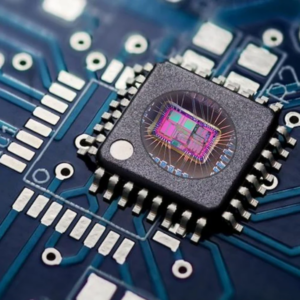

The PIC18F2620 microcontroller is a popular choice for embedded systems due to its robust performance and versatility. However, many manufacturers secure their firmware by locking the microcontroller, making it challenging to extract, recover, or replicate the source code. This article explores the methods and challenges associated with cracking or decrypting the protected memory of a locked PIC18F2620.

When dealing with a secured microcontroller, the first step is often to decapsulate the chip. This process involves removing the outer layer of the MCU to access the internal flash and EEPROM memory. Once exposed, specialized tools can be used to dump the binary data stored in the memory. However, this method is invasive and can damage the chip if not done correctly.

Pentru abordări non-invazive, atacatorii pot încerca să pirateze microcontrolerul exploatând vulnerabilitățile din programul său. Tehnici precum defecțiunea alimentării sau manipularea ceasului pot rupe uneori protecția criptată, permițând accesul la firmware. Odată ce protecția este ocolită, codul sursă poate fi extras și analizat.

For non-invasive approaches, attackers may attempt to hack the microcontroller by exploiting vulnerabilities in its program. Techniques such as power glitching or clock manipulation can sometimes break the encrypted protection, allowing access to the firmware. Once the protection is bypassed, the source code can be extracted and analyzed.

Another method involves cloning the microcontroller by copying the data from the flash and EEPROM. This requires advanced equipment and expertise, as the protected memory must be decrypted before it can be replicated. The recovered file or archive can then be used to program a new microprocessor, effectively creating a duplicate of the original device.

In conclusion, extracting the locked source code from a PIC18F2620 microcontroller is a complex task that requires specialized knowledge and tools. Whether through decapsulation, hacking, or cloning, the process involves overcoming significant security measures. As technology advances, so do the methods to attack and recover secured firmware, making it a constant battle between protection and exploitation.

On transitions from RC_RUN mode to PRI_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs by Extract Locked Microcontroller PIC18F2620 Source Code. When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock.

The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled. The power-managed Sleep mode in the PIC18F2620 devices is identical to the legacy Sleep mode offered in all other PICmicro devices.

Sonuç olarak, PIC18F2620 mikrodenetleyicisinden kilitli kaynak kodunu çıkarmak, özel bilgi ve araçlar gerektiren karmaşık bir görevdir. İster kapsülden çıkarma, ister bilgisayar korsanlığı veya klonlama yoluyla olsun, süreç önemli güvenlik önlemlerinin üstesinden gelmeyi içerir. Teknoloji ilerledikçe, güvenli donanım yazılımına saldırma ve kurtarma yöntemleri de gelişir ve bu da koruma ile istismar arasında sürekli bir savaşa dönüşür.

It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared only after the process of Microcontroller PIC16C620A Firmware reading has been completed. Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run. When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready, or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled in order to Copy Locked PIC16C65B Program (see Section 19.0 “Special Features of the CPU”).

In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.