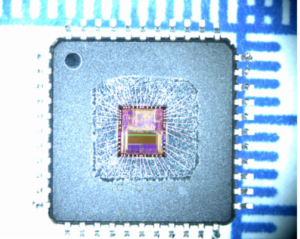

Copy Content of MCU PIC18F6390 Eeprom memory and flash memory, program and data in the format of binary or heximal of microcontroller pic18f6390 can be attacked;

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 16-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTC<2> and PORTD<7:5> data latches.

The TRISC<2> and TRISD<7:5> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs. In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows user to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle when copy hex from MCU.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in a time interval of 4 TOSC * (Timer2 Prescale Value) before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS1:T2CKPS0 bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive after copy software from Chip flash.

Note that in the Full-Bridge Output mode, the CCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

The direction of the PWM output changes when the duty cycle of the output is at or near 100%. The turn-off time of the power switch, including the power device and driver circuit to Break IC, is greater than the turn-on time.Figure 16-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle.

At time t1, the outputs P1A and P1D become inactive, while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 16-7), for the duration of ‘t’. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward before the code of Microcontroller can be copied.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

Reduce PWM for a PWM period before changing directions.

Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.