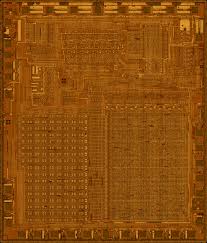

We can Extract Microprocessor PIC16C72A Heximal, please view the Microprocessor PIC16C72A features for your reference:

The prescaler assignment is fully under software control (i.e., it can be changed “on-the-fly” during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 5-1 and Example 5-2) must be executed when changing the prescaler assignment from Timer0 to WDT when extract microprocessor pic16c72a.

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 5-2. This precaution must be taken even if the WDT is disabled.

The PIC16F917/916/914/913 has a 16-bit timer. Figure 6-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features from heximal extraction:

16-bit timer/counter (TMR1H:TMR1L)

Readable and writable

Internal or external clock selection

Synchronous or asynchronous operation

Interrupt-on-overflow from FFFFh to 0000h

Wake-up upon overflow (Asynchronous mode)

Optional external enable input:

– Selectable gate source: T1G or C2 output (T1GSS)

– Selectable gate polarity (T1GINV) before extract microprocessor heximal

- Optional LP oscillator

The Timer1 Control register (T1CON), shown in Register 6-1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Timer1 can operate in one of three modes:

• 16-bit timer with prescaler

• 16-bit synchronous counter

• 16-bit asynchronous counter of pic16c72a heximal microprocessor

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In the Timer1 module, the module clock can be gated by the Timer1 gate, which can be selected as either the T1G pin or Comparator 2 output after microprocessor extraction.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKO), Timer1 can use the LP oscillator as a clock source. The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h.

When Timer1 rolls over, the Timer1 Interrupt Flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

• Timer1 Interrupt Enable bit (PIE1<0>)

• PEIE bit (INTCON<6>)

• GIE bit (INTCON<7>)

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine when pic16c72a heximal extraction.

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable;

however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.