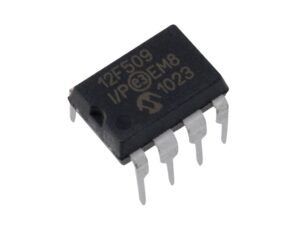

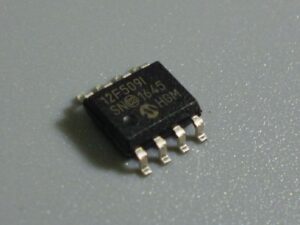

Extract IC PIC12F509 Heximal from its memory which include flash and eeprom, recover MCU content from memory will help to clone microcontroller fully functions;

After generating a START condition, the bus master transmits a control byte consisting of a slave address and a Read/Write bit that indicates what type of operation is to be performed.

The slave address consists of a 4-bit device code (1010) followed by three don’t care bits. The last bit of the control byte determines the operation to be performed if mcu firmware can be read.

When set to a one a read operation is selected, and when set to a zero a write operation is selected. (Figure 7-5). The bus is monitored for its corresponding slave address all the time.

It generates an acknowledge bit if the slave address was true and it is not in a programming mode. Following the start signal from the master, the device code (4 bits), the don’t care bits (3 bits), and the R/W bit (which is a logic low) are placed onto the bus by the master transmitter after Extract IC attiny15 software.

This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the master is the word address and will be written into the address pointer.

Only the lower four address bits are used by the device, and the upper four bits are don’t cares. The address byte is acknowledgeable and the master device will then transmit the data word to be written into the addressed memory location if read mcu attiny26l program.

The memory acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals (Figure 7-7). After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written.

If a stop bit is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written.

If more than 8 data bits are transmitted before the stop bit is sent, then the device will clear the previously loaded byte and begin loading the data buffer again.

If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a VCC threshold detector circuit which disables the internal erase/write logic if the VCC is below minimum VDD. Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high.