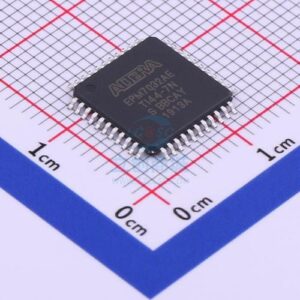

Altera CPLD EPM7032AETI44-7 Eeprom Firmware Copying is a process to crack the cpld protection by focus ion beam over its eeprom memory, and reverse engineer cpld chip epm7032aeti44 internal structure to locate its jed file;

Each LAB has 16 shareable expanders that can be viewed as a pool of uncommitted single product terms (one from each macrocell) with inverted outputs that feed back into the logic array.

Each shareable expander can be used and shared by any or all macrocells in the LAB to build complex logic functions. A small delay (tSEXP) is incurred when shareable expanders are used. Figure 3 shows how shareable expanders can feed multiple macrocells.

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions and through which will make the reading microchip process become easier.

Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB.

The compiler can allocate up to three sets of up to five parallel expanders to the macrocells that require additional product terms. Each set of five parallel expanders incurs a small, incremental timing delay (tPEXP).

For example, if a macrocell requires 14 product terms, the compiler uses the five dedicated product terms within the macrocell and allocates two sets of parallel expanders; the first set includes five product terms, and the second set includes four product terms, increasing the total delay by 2 ´ tPEXP in the process of copying heximal file from microchip.